Hardware TCP/IP-Stack

From the inventor of the W5100: "Unique Network Solution, It couldn't be Simpler, Stabler & Smarter! Fully Hardwired TCP/IP. Success belongs to you". WIZnet praises their so called "ioffload System" with the fact that it strongly unburdens an embedded MCU system. The system load through the TCP/IP-network decreases from 72% to 37% if, instead of a software, a hardware stack is used.

Summary of WIZnet hardware TCP/IP stacks

| Stack | Year | MCU-Bus | TCP/IP Core | Sockets / Tx- / Rx-Memory | Note |

| W3100A | 2002 | 8-bit | I | 4 / 8 kB / 8 kB | |

| W3150 / W3150A | 2005 | 8-bit | II | 4 / 8 kB / 8 kB | |

| W3150A+ | 2006 | 8-bit | II (modified) | 4 / 8 kB / 8 kB | |

| W5100 | 2007 | 8-bit | II (modified) | 4 / 8 kB / 8 kB | inchip Ethernet-Controller |

| W5300 | 2008 | 8/16-bit | II (modified) | 8 / 64 kB / 64 kB | inchip Ethernet-Controller and memory manager |

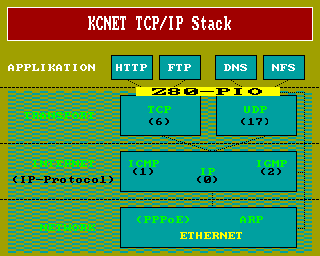

All WIZnet stacks replace the layers 1 to 3 of a common software TCP/IP stack with hardwired logic.

The W5100 used, is the last 8-bit-only stack with the following benefits:

- Performance:

- Line-Speed Data Transmission by Hardwired Logic

- up to 25 Mbps throughput at application layer

- Easy Implementation:

- Easy & Simple Control like Memory

- Save Development Time

- Cost Effectiveness:

- TCP/IP Implementation without OS

- MAC & PHY Embedded

WIZnet mentions the following key features:

- Support Hardwired TCP/IP Protocols: TCP, UDP, IP, ICMP, IGMP,IPv4 ARP, PPPoE, Ethernet

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full-duplex and Half-duplex)

- Support Auto MDI/MDIX (crossover detection)

- Support ADSL connection (with support PPPoE Protocol with PAP/CHAP Authentification mode)

- Support 4 independent sockets simultaneously

- No support of IP-Fragmentation

- Internal 16 kBytes Memory for Tx/Rx Buffers

- 0,18 µm CMOS technoloy

- 3,3 V operation with 5 V I/O signal tolerance

- small 80 Pin LQFP Package

- Lead-Free Package

- Support 3 different interfaces, direct memory access, indirect memory access and SPI Mode 0 and 3

- Multi-function LED outputs (Tx, Rx, Full/Half duplex, Collision, Link, Speed)

The KC85 or a CP/M computer were not listed as target devices, but this piece of hardware met my requirements for the use as a TCP/IP-controller in an Ethernet network for my system almost perfectly. The next picture shows once again the familiar block diagram. This was the principle plan to integrate the TCP/IP stack in my system. All "green and yellow" protocols of a TCP/IP implementation run in the W5100. The only real obstacle was the physical connection with my Z80 system, see next section of this article.

All WIZnet stacks are like memory in a system. The control-interface is a set of hardware addresses, which are established by the hardware designer and then covered from the chip. The TCP/IP core-II is almost always the same in all chips, there are slight differences in the meaning of cells or bits of cells. WIZnet had to remove errors from the W3150 and modified some details in the successor W3150A. All alterations led to the modified core-II of the W3150A+ or W5100.

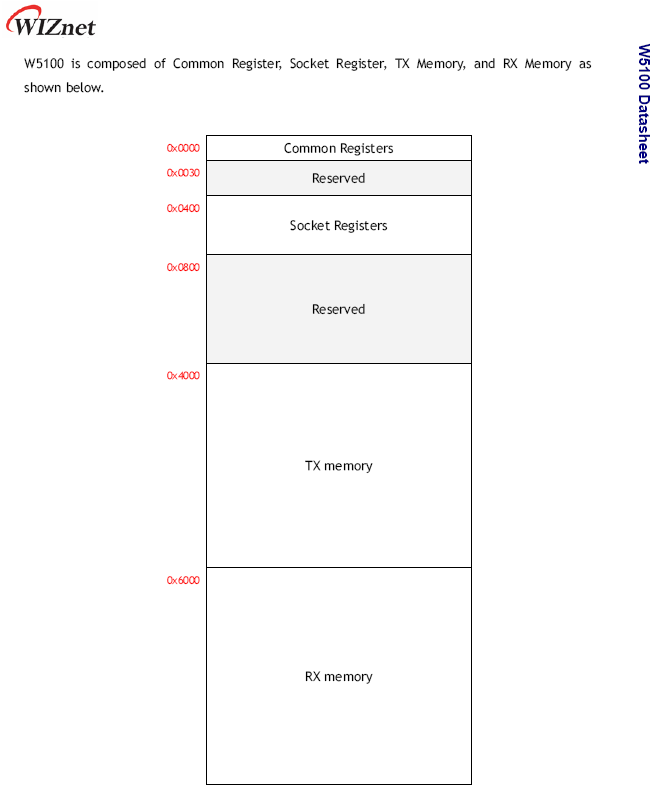

Because the W5100 is hardwired logic and not a device-interface of a software-controlled other system, there isn't any command set as usual. The W5100 is composed of 4 main memory areas which have defined tasks:

| Common Register | - stack operation mode - network configuration - interrupt behavior - TCP timing - socket memory configuration |

Base address + 0000H, 48 Bytes |

| Socket Register |

- socket operation mode |

Base address + 0400H, 4*256 Bytes per socket |

| Tx Memory | - Tx socket-memory Buffer (read/write) | Base address + 4000H, 8192 Bytes |

| Rx Memory | - Rx socket-memory Buffer (read only) | Base address + 6000H, 8192 Bytes |

Chapter 2 of the W5100 datasheet contains an example memory map. These addresses are valid if the base of the stack is 0000H in a real system:

Chapter 3 lists all accessible registers of the W5100 with address and name relative to address 0. In chapter 4, the functional description of all registers and their bits is carried out in detail : this is the most important chapter for the programmer of such a TCP/IP-stack. There are many explanations and state diagrams, which help to understand all functions.

Chapter 5 contains pseudocode for fundamental TCP/IP applications on the various layers, which such a stack has to do:

- TCP Server Mode

- TCP Client Mode

- UDP Mode

- IP Raw Mode

- Ethernet Raw Mode (MAC)

All of these pseudo-applications worked like expected. The Z80 code implementations are parts of the interface testprogram CPMNET.COM, and allow playing with a TCP/IP network without a higher protocol on the TCP-, UDP-, IP- and MAC-layer of the stack.

The not mentioned chapters of the datasheet describe all pins of the chip, possible hardware applications, electrical-, solder- and package-specifications. Since a ready-made network module is used, that is not of interest here.